## **FASTSERIES**

# FASTCAMERA CCD USER AND REFERENCE MANUAL

FVM-00406

## **COPYRIGHT NOTICE**

#### Copyright @ 2010 by FastVision LLC.

All rights reserved. This document, in whole or in part, may not be copied, photocopied, reproduced, translated, or reduced to any other electronic medium or machine-readable form without the express written consent of FastVision LLC.

FastVision makes no warranty for the use of its products, assumes no responsibility for any error, which may appear in this document, and makes no commitment to update the information contained herein. FastVision LLC. retains the right to make changes to this manual at any time without notice.

Document Name: FastCamera CCD User and Reference Manual

Document Number: FVM-00406

Revision History: 1.0 August 2010

#### Trademarks:

FastVision® is a registered trademark of FastVision LLC.

Channel Link™ is a trademark of National Semiconductor

Virtex™ is a trademark of Xilinx Inc.

Windows™, Windows 95™, Windows 98™, Windows 2000™, Windows NT™, and Windows XP™ are trademarks of Microsoft

All trademarks are the property of their respective holders.

FastVision LLC. 131 Daniel Webster Highway, #529 Nashua, NH 03060 USA

> Telephone: 603-891-4317 Fax: 603-891-1881

> > Web Site:

http://www.Fast-Vision.com/

Email:

sales@Fast-Vision.com, or support@Fast-Vision.com

## **TABLE OF CONTENTS**

| PURPOSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TABLE OF CONTENTS            | 3  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

| SENSORS         5           BOARD INTERCONNECTIONS         5           Power Bus         5           Scrial Channel         6           Video Channel         6           SENSOR BOARD         7           Block Diagram         7           Sensor Board PFGA         8           CPU BOARD         9           Block Diagram         9           CPU Board FPGA         10           I/O BOARD         11           Block Diagram         11           I/O Board FPGA         12           INTERFACE CONNECTORS         12           Power Connector         12           Power Requirements         12           Camera Link Connector         13           GigE connector         13           TJTAG Connectors         14           CAMERA OPTIONS         14           GAMERA OPTIONS         14           GISC VISION INTERFACE         14           Boot         15           Discovery         15           Command and Control Connections         15           Streaming Connections         15           Streaming Connections         15           Streaming Connectio       | PURPOSE                      | 5  |

| BOARD INTERCONNECTIONS   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CAMERA BOARDS BLOCK DIAGRAMS | 5  |

| BOARD INTERCONNECTIONS   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SENSORS                      | 5  |

| Power Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |    |

| Serial Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |    |

| SENSOR BOARD       7         Block Diagram       7         Sensor Board FPGA       8         CPU BOARD       9         Block Diagram       9         CPU Board FPGA       10         WO BOARD       11         Block Diagram       11         LO Board FPGA       12         INTERFACE CONNECTORS       12         Power Connector       12         Power Requirements       12         Camera Link Connector       13         GigE connector       13         TIAG Connectors       14         CAMERA OPTIONS       14         GIGE VISION INTERFACE       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CCT to CC4 inputs       15         ANALOG INTERFACE       16         Serial Interface       16         Serial Interface       16                                                                                    |                              |    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Video Channel                | 6  |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SENSOR BOARD                 | 7  |

| CPU BOARD       9         Block Diagram       9         CPU Board FPGA       10         WO BOARD       11         Block Diagram       11         I/O Board FPGA       12         INTERFACE CONNECTORS       12         Power Connector       12         Power Requirements       12         Camera Link Connector       13         Gig Connector       13         JTAG Connectors       14         CAMERA OPTIONS       14         GIGE VISION INTERFACE       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         Serial Interface       16         Soft WARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20                                                                    |                              |    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Sensor Board FPGA            | 8  |

| CPU Board FPGA       10         VO BOARD       11         Block Diagram       11         I JO Board FPGA       12         INTERFACE CONNECTORS       12         Power Connector       12         Power Requirements       12         Camera Link Connector       13         GigE connector       13         JTAG Connectors       14         CAMERA OPTIONS       14         GIGE VISION INTERFACE       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Streaming Connections       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Scrial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         C                                                  | CPU BOARD                    | 9  |

| I/O BOARD.       11         Block Diagram.       11         I/O Board FPGA.       12         INTERFACE CONNECTORS.       12         Power Connector       12         Power Requirements.       12         Camera Link Connector.       13         GigE connector       13         JTAG Connectors.       14         CAMERA OPTIONS.       14         GIGE VISION INTERFACE.       14         Boot.       15         Discovery.       15         Command and Control Connections.       15         Streaming Connections.       15         Streaming Connections.       15         Triggering.       15         CAMERA LINK INTERFACE.       15         Channel Link       15         Serial Link       15         CCI to CC4 inputs.       15         ANALOG INTERFACE.       15         SPECIAL INTERFACES       16         Serial Interface.       16         Motor Controller Output.       16         Isolated input and outputs.       16         SOFTWARE AND FIRMWARE.       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS.       18 </td <td></td> <td></td> |                              |    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CPU Board FPGA               | 10 |

| I/O Board FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O BOARD                    | 11 |

| INTERFACE CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |    |

| Power Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |    |

| Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |    |

| Camera Link Connector       13         GigE connector       13         JTAG Connectors       14         CAMERA OPTIONS       14         GIGE VISION INTERFACE       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CCI to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                            |                              |    |

| GigE connectors       13         JTAG Connectors       14         CAMERA OPTIONS       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                             | 1                            |    |

| JTAG Connectors       14         CAMERA OPTIONS       14         Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                          |                              |    |

| GIGE VISION INTERFACE.       14         Boot       15         Discovery.       15         Command and Control Connections.       15         Streaming Connections.       15         Events.       15         Triggering.       15         CAMERA LINK INTERFACE.       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs.       15         ANALOG INTERFACE.       15         SPECIAL INTERFACES.       16         Serial Interface       16         Motor Controller Output.       16         Isolated input and outputs.       16         SOFTWARE AND FIRMWARE.       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS.       18         SENSOR BOARD.       20         CPU BOARD.       24                                                                                                                                                                                                                                                                                                                                    |                              |    |

| GIGE VISION INTERFACE.       14         Boot       15         Discovery.       15         Command and Control Connections.       15         Streaming Connections.       15         Events.       15         Triggering.       15         CAMERA LINK INTERFACE.       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs.       15         ANALOG INTERFACE.       15         SPECIAL INTERFACES.       16         Serial Interface       16         Motor Controller Output.       16         Isolated input and outputs.       16         SOFTWARE AND FIRMWARE.       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS.       18         SENSOR BOARD.       20         CPU BOARD.       24                                                                                                                                                                                                                                                                                                                                    | CAMERA OPTIONS               | 14 |

| Boot       15         Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                           |                              |    |

| Discovery       15         Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |    |

| Command and Control Connections       15         Streaming Connections       15         Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |    |

| Events       15         Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |    |

| Triggering       15         CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e                            |    |

| CAMERA LINK INTERFACE       15         Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |    |

| Channel Link       15         Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |    |

| Serial Link       15         CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                              |    |

| CC1 to CC4 inputs       15         ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |    |

| ANALOG INTERFACE       15         SPECIAL INTERFACES       16         Serial Interface       16         Motor Controller Output       16         Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                              |    |

| SPECIAL INTERFACES         16           Serial Interface         16           Motor Controller Output         16           Isolated input and outputs         16           SOFTWARE AND FIRMWARE         16           FCCM PROGRAM         16           COMMAND AND CONTROL CELLS         18           SENSOR BOARD         20           CPU BOARD         24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                            |    |

| Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |    |

| Motor Controller Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |    |

| Isolated input and outputs       16         SOFTWARE AND FIRMWARE       16         FCCM PROGRAM       16         COMMAND AND CONTROL CELLS       18         SENSOR BOARD       20         CPU BOARD       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |    |

| FCCM PROGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |    |

| FCCM PROGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SOFTWARE AND FIRMWARE        | 16 |

| COMMAND AND CONTROL CELLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FCCM PROGRAM                 | 16 |

| SENSOR BOARD20 CPU BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |    |

| CPU BOARD24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |    |

| <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |    |

| XIO Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XIO Registers                |    |

| CPU Board Process Cell API                  | 26 |

|---------------------------------------------|----|

| FC XXX CPU FIRMWARE                         | 26 |

| VIDEO-BUS AND MESSAGE-BUS                   | 26 |

| CPU video in/out and message handling       | 26 |

| FgpiSrvHandler                              | 26 |

| FgpoSrvHandler                              | 27 |

| rtcell routing of video                     | 27 |

| example of vi + vo + routing of video-cells | 27 |

| MsgSrvHandler                               | 27 |

| Read, write and read-response.              | 28 |

| I/O-board opto-electronics change of state  | 28 |

| Write-requests                              | 28 |

| Read-requests                               | 28 |

| Read-response-request                       | 28 |

| Uart receive chars                          | 28 |

| Uart transmit chars                         | 29 |

| Sending cell – messages                     | 29 |

| command_sensreg_api                         |    |

| command_ioreg_api                           | 30 |

| API – FUNCTIONS                             | 30 |

| GetRoi_api                                  | 30 |

| SetRoi_api                                  |    |

| GetFrameControl_api                         |    |

| CaptureOneFrame_api                         |    |

| CaptureContinousFrame_api                   |    |

| GetFpgaRevID_api                            |    |

| SetShowUartMode_api                         |    |

| setupCpuStorageReadOut_api                  |    |

| MsgSrvStart_api                             | 32 |

| I/O BOARD FIRMWARE                          | 32 |

| SIZE AND COOLING                            | 34 |

| TROUBLESHOOTING                             | 35 |

| FASTVISION TECHNICAL SUPPORT                | 36 |

| CONTACTING TECHNICAL SUPPORT                | 36 |

## **PURPOSE**

This manual describes the architecture and use of the 'Kodak Fast Camera' camera family.

## CAMERA BOARDS BLOCK DIAGRAMS

This document applies to the FC105, FC205, FC215, and FC405.

## **SENSORS**

FCxxx camera is designed to be compatible with the 1, 2, 4, and 8 Mpixel Kodak Sensors.

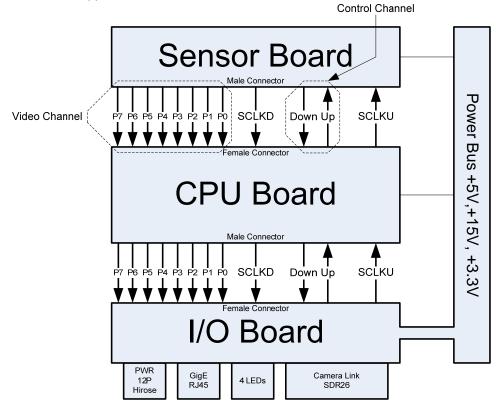

#### **BOARD INTERCONNECTIONS**

#### **Power Bus**

Running up to stack of boards is the power bus. The power bus is driven by the I/O board at the bottom of the stack. The power bus uses an eleven pin SIP connector with the male pins being soldered into the I/O board, while the other boards have pass through female connectors allowing the male pins to extend up through the whole stack of boards. This connection method limits the number of connector pin contacts between the power supply and the boards to one contact. The 11 pins in the power bus are:

| Pin | Function             |

|-----|----------------------|

| 1   | +15 Volts            |

| 2   | +/-15 Volt<br>Return |

| 3   | -15 Volts            |

| 4  | Ground     |

|----|------------|

| 5  | Ground     |

| 6  | +5 Volts   |

| 7  | +5 Volts   |

| 8  | Ground     |

| 9  | Ground     |

| 10 | +3.3 Volts |

| 11 | +3.3 Volts |

The I/O board has a power converter which provides the +3.3 volts to the bus from the +5 volt from the power brick. +15 Volts currently comes from the external power brick . .

#### **Serial Channel**

There is a bidirectional serial channel which passes through each board in the stack. The sensor board and the I/O board have receivers and transmitters while the inner CPU boards contain a receiver and transmitter for each direction. The serial channel operates at 320 Mb/sec and is re-timed at each board. The serial channel is implemented with a source synchronous clock, so the transmitters provide the clock to the receivers on the next board, above or below. A total of four signals are used, clock and data, for each direction. The serial cannel implements a 16 bit synchronous protocol using the value 0xA55A as an idle SYNC word. The serial channel sends 'Cells' which are from 2 to 17 words (16 bits) long. See the section below for the details of this protocol.

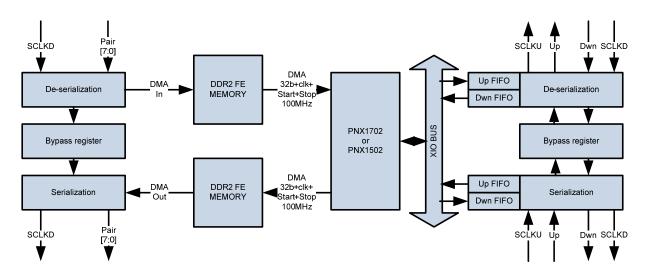

#### Video Channel

The video channel is a sixteen bit parallel data channel. This channel is implemented as 16 single ended data bits in 8 pairs (P0 to P7 in the figure) with a clock frequency of 160 MHz. The video channel is unidirectional and is sourced at the sensor board. Each board in the stack receives and retimes the video and retransmits it to the next board in the stack. The I/O board at the bottom of the stack receives the video and converts it to the output type implemented for the camera (GigE, Camera Link, or Analog). The video channel operates at 160 MHz single clock per data. This provides bandwidth for the four 16 bit pixel channels (taps) at 40 MHz each.

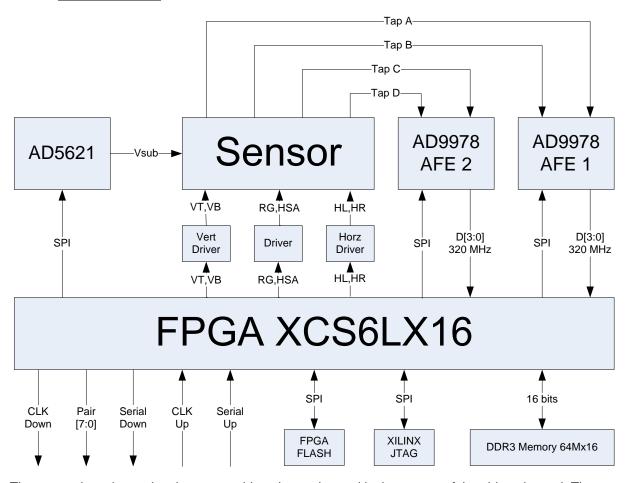

#### SENSOR BOARD

#### **Block Diagram**

The sensor board contains the sensor drive electronics and is the source of the video channel. The sensor board performs the following steps:

- 1. The FPGA decides based on the trigger mode and exposure how to operate the sensor.

- 2. The FPGA generates the driving clocks which operate the sensor in the selected mode for example four tap mode.

- 3. The sensor detects the light hitting its pixels and provides an analog signal to the Analog front end chips (AFE1 and AFE2).

- 4. The AFE chips convert the analog signal from the sensor to 14 bit digital values which are representative of the light hitting the sensor.

- 5. The FPGA re-orders the taps coming from the sensor as it writes the pixels into a frame buffer, to create a raster ordered array of pixels in the buffer memory.

- 6. When the frame is complete, the FPGA swaps buffers and begins reading out the pixels in raster order from the frame buffer just completed.

- 7. The FPGA does dark and bright field correction on the pixels using a table stored in the buffer memory.

- 8. The corrected pixels are sent in 'Cells' (small packets) down the video channel to the next board in the stack.

The sensor board is essentially 'the camera' part of the FC205 camera. If the camera is built with a CPU board, it is a 'smart' camera. The I/O board provides protocol conversion from the parallel format of the video channel, to GigE, Camera Link, and Analog.

The flash on the FPGA is 128 Mbits. It contains the bit stream for booting the FPGA, a script for initializing the sensor board, and an array of correction coefficients for dark and bright field correction of the sensor image. The sensor can be operated in three modes, one tap, two taps and four tap modes. The taps read out from the corners of the sensor.

In one tap mode the sensor is read out in raster order from bottom to top (correcting for the Lens inversion). In two tap mode the sensor can be split into two pieces. One split is into a left and right half of the sensor; the other split is top and bottom half of the sensor. In the left and right split, the sensor is read out from the bottom on the left and the right corners. The right half is read out reversed left to right, which the FPGA corrects by writing the values to the memory buffer in reverse address order. In the top and bottom readout mode, the top part is read out last line first, so the FPGA writes the lines in reverse order to the buffer, building the image in the buffer memory in raster order.

Finally in four tap mode the sensor is read out from the four corners of the image array. The bottom left reads out in order, the bottom right reads the lines reversed end to end, the top left reads out with the lines in reverse order top to bottom, and the top right tap reads out the lines reversed end to end, and the last line first.

The FPGA corrects the reversals while writing the pixels to the memory buffer. When the buffer swap occurs, the FPGA reads out the in order image and applies the correction factors. The 14 bit pixels have 14 bit values subtracted from them to do the dark field correction. If the resulting pixel value would be negative it is set to zero. Next the dark field corrected pixels are multiplied by a 14 bit gain coefficient, producing a 28 bit result. The 28 bits are shifted right by a programmable amount. If the upper 12 bits of the shifted result are non-zero then the pixel value is set to all ones. The lower 16 bits are the pixel value sent by the sensor board down the stack on the video channel. By selecting the amount of shift performed the binary point of the gain coefficient is positioned. In the machine vision community the dark field correction is sometimes called the PSNU or DSNU which are acronyms for Photo-receptor Static Non-Uniformity or Dark Signal Non-Uniformity. The gain correction is sometimes called the PRNU which stands for Photo-receptor Response Non-Uniformity.

#### **Sensor Board FPGA**

The sensor FPGA block diagram is shown above.

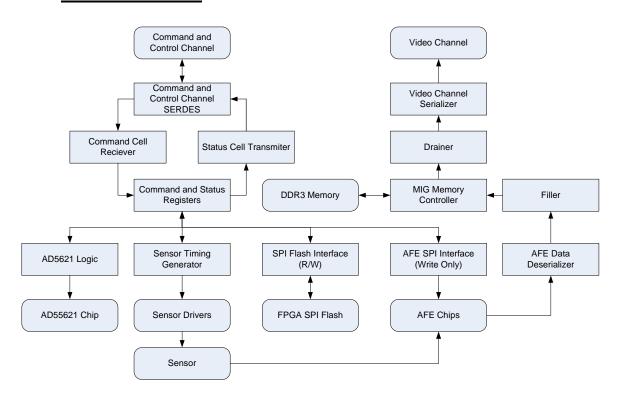

#### **CPU BOARD**

#### **Block Diagram**

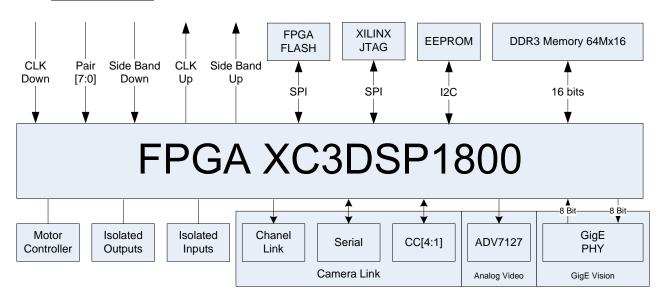

A block diagram of the CPU board is shown above. The CPU board is designed to process video from the sensor board (or any board above it in the stack). The CPU board is used in 'smart' camera applications. The CPU can process video, and control all the features supported by the camera, which include sending video to the output, toggle outputs, monitor inputs, sends data to the serial interface or to the GigE interface. The CPU boots from an EEPROM via I2C. The boot loads and executes a program from the 64MB NOR flash. The NOR Flash can be read or written by the processor so that parameter and result data can survive power failures. The CPU can receive video from the stack above it, modify the video and send the modified video down to the next board in the stack.

#### **CPU Board FPGA**

A block diagram of the CPU FPGA is shown above.

The video interface can operate in three modes.

- The first mode is the video can completely bypass the CPU card without going to the CPU. This is the default mode which is used during booting of the CPU.

- The second mode is the video can be sent to the CPU and at the same time forwarded to the

next board in the stack. This mode is used when the CPU is processing the video at the same

time it is being output to the board below.

- The third mode the CPU receives the video from the board above, and provides video to the board below. This mode is used when the CPU must modify the video in some way.

The serial channel operates by passing cells up or down the stack which are not targeted for the CPU board FPGA or the CPU. The destination of the cell determines which direction it is routed. Cells that target the FPGA on the CPU board read and write registers in the FPGA. Cells that target the CPU are placed in an input FIFO and can be read by the CPU. In turn the CPU can send cells which can target any of the other boards in the stack. The capability of the CPU to send and receive arbitrary cells gives it control of all the registers in the camera.

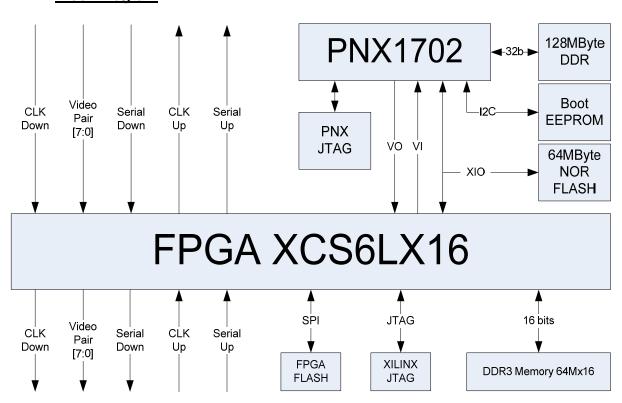

#### I/O BOARD

#### **Block Diagram**

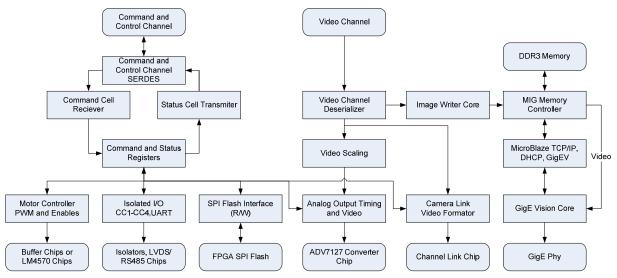

The I/O board provides interfaces to the world outside the camera. Several interfaces are provided, which can be controlled by the CPU board if it is present, or in dumb camera applications the interfaces are configured to respond as requested by the customer, for example the camera link interface receives the video from the sensor board when a dumb camera link camera is required. The motor controller contains 3 DC motor controllers which can be used to drive small DC motors. The board uses National Semiconductor LM570 motor controllers. There are 6 optically isolated I/O pins can all be configured as outputs. Four of the isolated I/Os can be configured as inputs. The isolated I/O pins use PS2801-1 opto-isolators. The outputs can switch a maximum of 50 ma, and can tolerate up to 80 volts (when off). The outputs provide a 47 ohm resistor and a protection diode in series with the opto-isolators transistor. The optically isolated inputs can tolerate up to 75 volts, and are current limited to 20ma. The input on threshold is 5 volts. The input off threshold is below 1 volt.

The Camera Link interface provides a base camera link configuration. The serial port defaults to 9600 baud and can be programmed to higher baud rates (up to 115,200 baud). The CC1 signal is configured as a trigger input on the dumb camera. On the smart camera they can be configured as inputs or outputs, using LVDS or RS485 style drivers and receivers (order option). The ADV7127 is a 10 bit DAC which can be used to generate a one volt analog video output which is RS343 sync on green compatible. The ADV7127 can be clocked at up to 240 MHz. The GigE interface uses a Marvel 88E1111 phy. The FPGA can be ordered with GigE vision compatible firmware allowing the camera to interoperate with other GigE vision cameras, or it can be used in a smart camera as a gigabit Ethernet interface by the CPU.

#### **I/O Board FPGA**

The diagram above shows the I/O board FPGA Firmware.

## **INTERFACE CONNECTORS**

#### **Power Connector**

The power connector is a Hirose 12 pin cylindrical connector HR10A-10R-12PB. The pin out of the connector is application dependent and is shown in the table below.

| Pin | Option 1         | Option 2       | Option 3                                |

|-----|------------------|----------------|-----------------------------------------|

| 1   | Ground           | Ground         | Ground                                  |

| 2   | +5 Volts In      | +5 Volts In    | +5 Volts Input Power                    |

| 3   | -15 Volts In     | GPIO to Sensor | -15 Volts (May be changing to optional) |

| 4   | +15 Volts In     | +15 Volts In   | +15 Volts (May be changing to optional) |

| 5   | Motor 3 negative | +/-15V Ground  | Ground                                  |

| 6   | Motor 1 positive | CC1 positive   | No Connection                           |

| 7   | Motor 1 negative | CC1 negative   | No Connection                           |

| 8   | Motor 3 positive | Ground         | Ground                                  |

| 9   | Motor 2 positive | CC2 Positive   | No Connection                           |

| 10  | Ground           | Ground         | Ground                                  |

| 11  | +5 Volts In      | +5 Volts In    | +5 Volts Input Power                    |

| 12  | Motor 2 negative | CC2 negative   | No Connection                           |

#### **Power Requirements**

<sup>+5</sup> Volts at 3 amps max.

<sup>+15</sup> Volts at 100 ma max.

Typical power dissipation for the CPU version is 14 watts.

#### **Camera Link Connector**

The camera can be built with a SDR26 connector which can be used to provide a base Camera Link interface, or it can be used to provide general purpose I/O. The optically Isolated I/O is optionally provided on this connector. The pin out of this connector is:

| Pin | Signal               | Optional                 | Optional                  | Signal               | Pin |

|-----|----------------------|--------------------------|---------------------------|----------------------|-----|

| 1   | Ground               | Ground                   | Ground                    | Ground               | 14  |

| 2   | Tx Out 0<br>Negative | Optical Out 0 Positive   | Optical Out 0<br>Negative | Tx Out 0 Positive    | 15  |

| 3   | Tx Out 1<br>Negative | Optical Out 1 Positive   | Optical Out 1<br>Negative | Tx Out 1 Positive    | 16  |

| 4   | Tx Out 2<br>Negative | Not used                 | Not used                  | Tx Out 2<br>Positive | 17  |

| 5   | Tx Clock<br>Negative | Not used                 | Not used                  | Tx Clock<br>Positive | 18  |

| 6   | Tx Out 3<br>Negative | Not used                 | Not used                  | Tx Out 3<br>Positive | 19  |

| 7   | Sertc Positive       | RS485 Rx Positive        | RS485 Rx<br>Negative      | Sertc Negative       | 20  |

| 8   | Sertfg Negative      | RS485 TxNegative         | RS485 Tx<br>Negative      | Sertfg Positive      | 21  |

| 9   | CC1 Negative         | Optical In 0<br>Negative | Optical In 0<br>Positive  | CC1 Positive         | 22  |

| 10  | CC2 Positive         | Optical In 1<br>Positive | Optical In 1<br>Negative  | CC2 Negative         | 23  |

| 11  | CC3 Negative         | Optical In 2<br>Negative | Optical In 2<br>Positive  | CC3 Positive         | 24  |

| 12  | CC4 Positive         | Optical In 3<br>Positive | Optical In 3<br>Negative  | CC4 Negative         | 25  |

| 13  | Ground               | Ground                   | Ground                    | Ground               | 26  |

The optical isolated inputs can be configured as additional outputs if required. Be aware that the positive and negative connections are as indicated for historical reasons relating to the history of the Camera Link interface. Be absolutely sure how your camera is configured before connecting to this connector. This connector can be configured in many ways one pin pair at a time.

#### **GigE** connector

The GigE connector is a standard RJ45 connector for use with UTP CAT5E or CAT6 cable. Its pin out follows the Ethernet standards and is given here for reference.

| Pin | Signal |

|-----|--------|

| 1   | A+     |

| 2   | Α-     |

| 3   | B+     |

| 4   | C+     |

| 5   | C-     |

| 6   | B-     |

| 7   | D+     |

| 8   | D-     |

|     |        |

#### **JTAG Connectors**

Inside the camera are JTAG connectors for connection to Xilinx and CPU JTAG controllers / cables. The JTAG connectors use two small connectors. The pin out of the JTAG connects is board dependent but follows the following table generally:

| Pin  | Pin FPGA Signal CPU Sign |            |

|------|--------------------------|------------|

| Ja-1 | Ground                   | Ground     |

| Ja-2 | TDO                      | TDO        |

| Ja-3 | TMS                      | TDI        |

| Ja-4 | NC                       | RESET~     |

| Jb-1 | Ground                   | Ground     |

| Jb-2 | TCK                      | TCK        |

| Jb-3 | TDI                      | TMS        |

| Jb-4 | +3.3 Volts               | +3.3 Volts |

The standard camera does not provide access to these connectors. Please contact the factory should you wish access to these connectors.

Note: Opening the camera case violates the warrantee of the camera.

## **CAMERA OPTIONS**

The Camera can be purchased with several different combinations of options. The standard configurations are Camera Link, GigE Vision, or Analog.

## **GIGE VISION INTERFACE**

The GigE interface provides TCP/IP access and GigE Vision access to the camera. GigE Vision standard 1.0 is supported by the camera.

#### **Boot**

On power up the camera gets its IP number via three different schemes. If a static IP has been programmed the camera uses the value programmed. If the camera has DCHP enabled an IP address will be obtained for a responding DCHP server. If the DCHP server does not respond, or if DCHP is disabled the camera will use Auto IP. Once the camera has an IP address it will wait for a discovery broadcast by a GigE Vision server on its subnet.

#### **Discovery**

The camera will respond to a discovery request as specified by the GigE Vision Standard. It is possible to bypass discovery and go directly to a command / control connection phase, if the camera is already known to a GigE server.

#### **Command and Control Connections**

A GigE server can make a command and control connection to the camera. Access to the required GigE vision registers and to the Cell interface to the camera is provided via the GigE vision interface.

#### **Streaming Connections**

The streaming interface supports a single channel of streaming data with packet sizes negotiable during connector, or with fixed packet sizes. In most applications it is not necessary to modify the packet size manually.

#### **Events**

The GigE interface supports Events. The camera can provide a triggered event, or an arbitrary event if the camera is a smart camera (has a CPU board).

#### **Triggering**

The camera may be triggered by hard wiring to the CC1, or opto input 0 interfaces. In addition the camera may be triggered via the GigE connection. Finally the camera may operate on an internal trigger generated by the CPU, or via the free running trigger option.

#### CAMERA LINK INTERFACE

The camera provides a standard base camera link interface. The format of the interface is programmable 8, 10, 12, 14 or 16 bits per pixel one tap, or 8, 10 or 12 bits two taps. CC1 is used as the trigger interface, and the serial link defaults to 9600 baud, no parity, 8 bits and one stop bit.

#### **Channel Link**

The channel link interface operates at 62.5 MHz typically, though this can be modified should the customer require.

#### **Serial Link**

The serial link follows the camera link standard and supports up to 115,200 Baud. The serial link receivers and drivers can be built with RS485 compatible drivers and receivers. Note, these two pairs do not support multi drop operation, that is the drivers are always enabled.

#### CC1 to CC4 inputs

The CC1 input is typically used for triggering, but all four of the inputs can be enabled as trigger sources should it be needed. These inputs can be used to signal the CPU in a smart camera application. Internally when these input change state a cell is sent to the sensor board to trigger a frame. The CC1 to CC4 inputs can be built with LVDS or RS485 drivers and receivers. In both cases direction and enable is provided, so these pins can implement bi-directional signaling, and true RS485 serial interfaces. Please contact the factory if you wish to use these pins as outputs.

#### ANALOG INTERFACE

The analog interface provides a RS343 compatible output which can be programmed to output the captured monochrome (or Bayer Pattern Monochrome) image as a VCBS (1 volt composite sync) analog signal. The characteristics are programmable via register 0x0010 to 0x0017 of the I/O board.

#### SPECIAL INTERFACES

Several special interfaces are provided.

#### **Serial Interface**

The serial interface is present in all versions of the camera. When the camera is powered up the serial interface provides access to the command and control channel in the camera, via a byte serial encoding of command and control Cells.

#### **Motor Controller Output**

The motor control outputs can be configured to drive DC motors directly, or provide a 50 Hz TTL PWM signal for use with servo motors. The pulse width is programmable from 1 to 2 msec in 256 steps.

#### **Isolated input and outputs**

The isolated inputs and outputs are provided on the SDR26 interface connector and replace camera link signals. The four inputs on the CC1-CC4 signals can be configured as optically isolated outputs. The two dedicated outputs use the channel link signals so if they are ordered the channel link interface is not supported

## SOFTWARE AND FIRMWARE

Several software and firmware components are available to support the use of the camera.

#### **FCCM PROGRAM**

The FCCM (Fast Camera Control Modular) program provides a direct interface to the Cell interface internal to the camera. The FCCM program uses the serial interface provided with the camera and accesses the serial interface using a camera link style serial interface DLL. The FCCM program uses a special mode of the I/O board FPGA so that it can send and receive cells on the internal serial channel of the camera.

| Subsystem | Command                             | Function                         |

|-----------|-------------------------------------|----------------------------------|

| fccm      | В                                   | Load Com DLL                     |

| fccm      | С                                   | Send a Cell                      |

| fccm      | F                                   | Terminal Mode                    |

| fccm      | V                                   | Set Verbosity                    |

| fccm      | X                                   | Exit Program                     |

| fccm      | ?                                   | Help                             |

| fccm      | !                                   | Dos command                      |

| fccm      | Timeout                             | Set timeout in msec              |

| sensor    | Sensd                               | Dump Sensor Registers            |

| sensor    | Sensreg                             | Read or Write to Sensor Register |

| sensor    | sspie <reg> [<value>]</value></reg> | Erase Sensor SPI Flash           |

| sensor    | Sspipf                              | Program file to Sensor SPI       |

| sensor | sspipm <list of="" values=""></list>                                    | Program manual data to Sensor<br>SPI   |  |

|--------|-------------------------------------------------------------------------|----------------------------------------|--|

| sensor | Sspid                                                                   | Display Sensor SPI data                |  |

| sensor | sspise <start address="" byte=""><end address="" byte=""></end></start> | Sensor SPI Sector Erase                |  |

| sensor | Sspiid                                                                  | Read Sensor SPI Id numbers             |  |

| sensor | sspi2f                                                                  | Output SPI contents to file            |  |

| sensor | Ogtr                                                                    | Offset Gain Table Read                 |  |

| sensor | Ogtw                                                                    | Offset Gain Table Write                |  |

| sensor | Ogtm                                                                    | Offset Gain Table Manual               |  |

| sensor | Afeinit                                                                 | Initialized AFE Registers              |  |

| sensor | Afew                                                                    | Write to AFE register                  |  |

| sensor | Afer                                                                    | Display last written value AFE         |  |

| sensor | Afem                                                                    | Set AFE debug mux                      |  |

| sensor | Afed                                                                    | Dump All AFE registers                 |  |

| sensor | Afetp                                                                   | Turn On/off AFE Test pattern           |  |

| sensor | Pboot                                                                   | Program register settings in SPI flash |  |

| sensor | ad5621 <5.0 to 15.0 float>                                              | Set Subtrate voltage(Ad5621 DAC)       |  |

| sensor | resolution <n cols=""><n rows=""></n></n>                               | Set Sensor Resolution                  |  |

| sensor | v1t <rising><falling></falling></rising>                                | Set V1T edge delays                    |  |

| sensor | v2t <rising><falling></falling></rising>                                | Set V2T edge delays                    |  |

| sensor | v3t <rising><falling></falling></rising>                                | Set V3T edge delays                    |  |

| sensor | v4t <rising><falling></falling></rising>                                | Set V4T edge delays                    |  |

| sensor | v1b <rising><falling></falling></rising>                                | Set V1B edge delays                    |  |

| sensor | v2b <rising><falling></falling></rising>                                | Set V2B edge delays                    |  |

| sensor | v3b <rising><falling></falling></rising>                                | Set V3B edge delays                    |  |

| sensor | v4b <rising><falling></falling></rising>                                | Set V4B edge delays                    |  |