# FASTMOTION STRETCH LIBRARY

FASTMOTION STRETCH LIBRARY USER'S MANUAL

## **COPYRIGHT NOTICE**

#### Copyright © 200-2007 by Alacron Inc.

All rights reserved. This document, in whole or in part, may not be copied, photocopied, reproduced, translated, or reduced to any other electronic medium or machine-readable form without the express written consent of Alacron Inc.

Alacron makes no warranty for the use of its products, assumes no responsibility for any error, which may appear in this document, and makes no commitment to update the information contained herein. Alacron Inc. retains the right to make changes to this manual at any time without notice.

| Document Name:    | Fast M | lotion User's Manual |

|-------------------|--------|----------------------|

| Document Number:  | 30002- | -00395               |

| Revision History: | 1.0    | Jan 25, 2003         |

|                   | 2.0    | April 10, 2003       |

|                   | 3.0    | April 10, 2007       |

#### Trademarks:

Alacron® is a registered trademark of Alacron Inc.

FastSeries® is a registered trademark of Alacron Inc.

**Solaris™** is a trademark of Sun Microsystems Inc.

Unix® is a registered trademark of Sun Microsystems Inc.

Windows™, Windows 95™, Windows 98™, Windows 2000™, Windows NT™, and Windows XP™ are trademarks of Microsoft

#### All trademarks are the property of their respective holders.

#### Alacron Inc.

71 Spit Brook Road, Suite 200

#### Nashua, NH 03060

#### USA

Telephone: 603-891-2750

#### Fax: 603-891-2745

Web Site: http://www.alacron.com/

Email:sales@alacron.com, or support@alacron.com

# TABLE OF CONTENTS

| 1. INT                                                       | RODUCTION                                                                                                                                                                                                         | 7                                             |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1.1<br>1.2<br>1.3                                            | PURPOSE<br>AUDIENCE<br>FASTMOTION STRETCH LIBRARY                                                                                                                                                                 | 8                                             |

| 2. LIB                                                       | RARY VERSIONS                                                                                                                                                                                                     | 8                                             |

| 1.4<br>1.5<br>1.6<br>1.7<br>1.8                              | INCLUDE FILE<br>DATA TYPES- MATRICES AND IMAGES<br>FASTMOTION LIBRARY REFERENCE<br>MEMORY USE.<br>API FUNCTIONS OF THE FASTMOTION LIBRARY                                                                         | 8<br>9<br>.10                                 |

| 3. FAS                                                       | ST-X UXGA FUNCTIONS                                                                                                                                                                                               | 18                                            |

| 1.9<br>1.10                                                  | API FUNCTIONS OF THE FASTMOTION UXGA OPTION LIBRARY                                                                                                                                                               | -                                             |

| 4. UX                                                        | GA CAPTURE CONTROL FILE CONTENT                                                                                                                                                                                   | .22                                           |

| 1.11<br>1.12<br>1.13<br>1.14<br>1.15<br>1.16<br>1.17<br>1.18 | [STRETCH] SECTION<br>[PLL] SECTION<br>[BUFFER.1] SECTION<br>[BUFFER.2] SECTION<br>[AFML] SECTION<br>[UXGA.1] AND [UXGA.2] SECTIONS<br>[CAPTURE.1] AND [CAPTURE.2] SECTIONS<br>[AD9888B.1 AND [AD9888B.2] SECTIONS | .23<br>.24<br>.24<br>.24<br>.24<br>.25<br>.26 |

| -                                                            | E AD9888 REGISTERS                                                                                                                                                                                                |                                               |

|                                                              | AD9888 CONTROL REGISTER DETAIL                                                                                                                                                                                    |                                               |

| 6. EX/                                                       | AMPLE SETTINGS                                                                                                                                                                                                    | .41                                           |

| 7. TUI                                                       | NING THE SETTINGS                                                                                                                                                                                                 | 42                                            |

| 8. GE                                                        | NERAL INFORMATION                                                                                                                                                                                                 | .44                                           |

| 1.20<br>1.21                                                 | TROUBLESHOOTING<br>ALACRON TECHNICAL SUPPORT                                                                                                                                                                      |                                               |

# OTHER ALACRON MANUALS

Alacron manuals cover all aspects of FastSeries hardware and software installation and operation. Call Alacron at 603-891-2750 and ask for the appropriate manuals from the list below if they did not come in your FastSeries shipment.

- 30002-00148 ALFAST Runtime Software Programmer's Guide & Reference

- 30002-00150 FastSeries Library User's Manual

- 30002-00153 Fast I/O Hardware User's Manual

- 30002-00155 FastMem Hardware User's Manual

- 30002-00162 FOIL FastSeries Object Imaging Library User's Manual

- 30002-00169 ALRT Runtime Software Programmer's Guide & Reference

- 30002-00170 ALRT, ALFAST & FASTLIB Software Installation Manual for Linux

- 30002-00171 ALRT, ALFAST, & FASTLIB Software Installation for Windows NT

- 30002-00173 FastMem Programmer's Guide & Reference

- 30002-00176 FastImage 1300 Hardware User's Manual

- 30002-00180 Fast4 1300 Hardware User's Manual

- 30002-00184 FastSeries Getting Started Manual

- 30002-00183 FastImage 1300 Camera Integration User's Manual

- 30002-00185 FastVision Hardware User's Manual

- 30002-00186 FastVision Software User's Manual

- 30002-00187 FastFrame 1300 Hardware User's Manual

## 1. INTRODUCTION

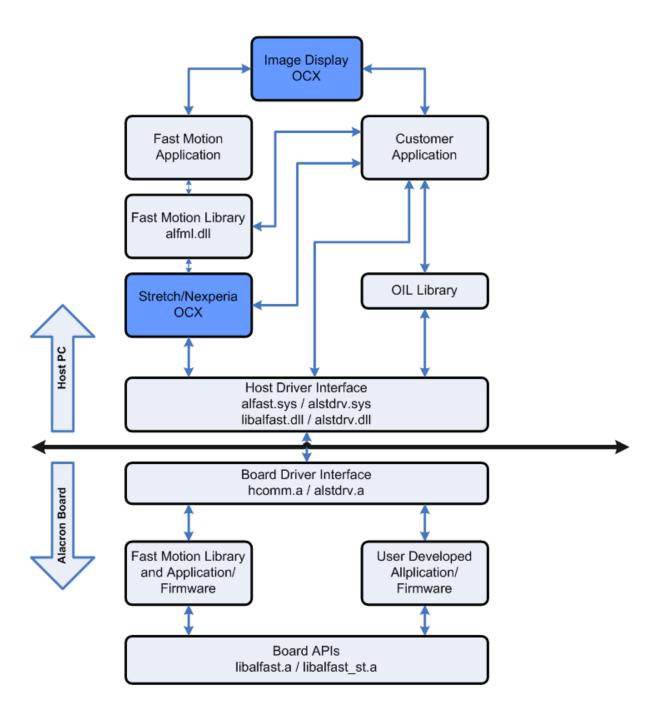

This manual covers the Alacron **FASTMOTION LIBRARY** software. The FASTMOTION LIBRARY enables the software developer to embed FASTMOTION functionality into their application. The FASTMOTION LIBRARY and Application use the OCX model for windows development as diagrammed below.

1.1 Purpose

The FastMotion Library provides calling specifications and descriptions for the Alacron FastMotion Library of fast image capture functions.

#### 1.2 <u>Audience</u>

This section of the manual is intended for technical personnel responsible for developing video capture application software to run in the host computer using Alacron boards. This manual assumes familiarity with operating system commands to configure the software and with the C programming language.

## 1.3 FASTMOTION STRETCH Library

The Alacron FastMotion Library for the FastSeries family of processor boards is based on Alacron Runtime (ALRT) software. The FastMotion Library enables capturing sequences of high frame rate images from a variety of digital and analog sources into system memory (RAM). The FastMotion Library supports developing capture application under Microsoft Windows XP and Linux.

This section provides an overview of the FastMotion Library data types and functions. Function calling sequences, return values and other specifics are provided in the next chapter.

## 2. LIBRARY VERSIONS

The FastMotion Library is distributed with a dynamically linked library for the host computer and with a set of board programs and capture profile files suitable for the different types of boards and input sources. Host programs that wish to use FastMotion Library functions should link to alfml.lib. In the Linux environment FastMotion Library is a staticly linked library alfml.a.

#### 1.4 Include File

Application programs using the FastMotion Library should include **<alfml.h>**, which is in the installation directory.

#### 1.5 Data Types- Matrices and Images

A matrix or image is a two-dimensional array of values defined by a pointer (or array address), a vertical stride, the number of rows and the number of columns. These values may either be real or complex. The vertical stride defines the address increment from one row of the array to the next, and allows the referencing of "sub-arrays" of the image. The FastMotion Library uses row-major order. Successive locations in memory contain successive elements of a row, until the end of the row, which is followed by the first element of the next row. If a program desires column-major order, swap the row and column input arguments to achieve the desired result.

#### 1.5.1 List of Functions

The FastMotion Library contains the following functions:

AlfmlOpen AlfmlClose AlfmlSetCallBack AlfmlSetCallBack AlfmlStartGrab AlfmlStopGrab AlfmlGetImage AlfmlGetImageIndex AlfmlGetLastImageIndex AlfmlGetErrorSize AlfmlGetLastError

The functions above are present in all versions of the FastMotion Library. Each specific product configuration can have additional interfaces.

#### 1.6 FastMotion Library Reference

This chapter provides detailed documentation on the functions in the FastMotion Library.

Each function is listed on a separate page showing input arguments, output arguments, and execution functionality. The functions that are part of the FastMotion Library are executed on the PC. The FastMotion Library supports users who do not want to develop software for the Stretch processor on the Fast-X/e boards. The FastMotion Library block diagram is show below.

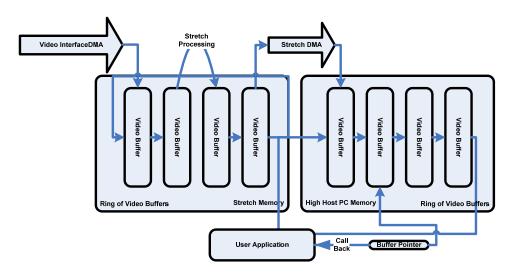

The data flows by successive DMA operations. Video data from the video source is DMAed into Stretch memory, in to a ring of buffers. At the same time the Stretch processor can be performing processing on a buffer to an output buffer. Again at the same time the Stretch DMA controller is transferring a completed

buffer to the host memory. The FastMotion Library traps an event from the Stretch processor which identifies the new filled buffer in memory. The thread in the FastMotion Library (not a user thread) makes a callback to a user provided callback function and provides a buffer index, which is turned into a buffer address by a separate API. Assuming all the DMAs and processors can keep up data flows.

In the case where data flow is faster than processing, the slow part does not process or transfer its current buffer, then the DMA or processing advances to the next buffer to output into, which if not available, the source buffer is dropped as though it had been empted by the transfer or DMA operation.

The buffer which is passed to the callback function is locked as long as the user application does not return from the callback. When the callback returns the FastMotion Library unlocks the buffer making it available for new data. The Depth of the ring buffers is settable up to the limit of available memory.

#### 1.7 <u>Memory Use</u>

The FastMotion Library uses memory blocked from use by the host operating system. This is done by telling the OS it can't use a block of memory, at the top of physical memory. On Windows this is done by modifying the file c:\boot.ini which is a hidden system file. On Linux this is done with a boot parameter to the loader.

The size of this memory block is determined by a user settable parameter called 'DMABUF\_LENGTH'.

Note: The FastMotion Library is not the only program that uses this method of obtaining some contiguous memory to do DMAs with. Several companies have used this method. Please be sure to check that the block of memory is not being used by some other program.

## 1.8 <u>API Functions of the FastMotion Library</u>

## AlfmlOpen

#### C Usage

int AlfmlOpen(char\* filename, imdev\_t\* fgrab)

#### Arguments

| filename | A valid path and file name of the capture profile file.                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| fgrab    | A handle to the frame grabber if it exists. This handle<br>must be used in other library functions that refer to the<br>same session. |

#### Description

This function attempts to find a frame grabber, to initialize it according the selected capture profile file and to establish a communication link between the frame grabber and the program.

#### **Return Values:**

On success, this function returns zero value and sets the fgrab variable to a valid handle. On failure, this function returns an error code and sets the fgrab variable to Null (zero). To get extended error information, call AlfmlGetLastError().

#### Example:

## AlfmIClose

#### C Usage

void AlfmlClose(imdev\_t fgrab)

#### Arguments

| Fgrab | A handle to the frame grabber that previously allocated with AlfmlOpen() function. |

|-------|------------------------------------------------------------------------------------|

|       |                                                                                    |

#### Description

Releases control of the frame grabber. After calling this function the fgrab handle is no longer valid.

## AlfmlSetCallback

#### C Usage

```

int AlfmlSetCallback(imdev_t fgrab, void* Func, void* userData)

```

#### Arguments

| fgrab    | A valid handle to the board previously allocated with AlfmIOpen() function.            |

|----------|----------------------------------------------------------------------------------------|

| Func     | Address of the callback function.                                                      |

| userData | Pointer to a user structure that will be returned to the user as a callback parameter. |

#### Description

Connects a callback function that will be fired every time an event received from the frame grabber is recieved. The event are received at the end of the buffer and after acquiring every imagePerEvent images.

The callback function definition is int AlfmlCallBack(int reason, void\* userData, int imageIndex)

The reason variable can be one of

AL\_IMAGE\_READY AL\_GRAB\_FINISHED AL\_STDOUT AL\_GRAB\_TIMEOUT

If the reason is AL\_IMAGE\_READY, then 'imageIndex' is the index of the just filled buffer in memory. Use AfmlGetImage to obtain an image pointer.

If the reason is AL\_GRAB\_FINISHED, then the cause of the call back was the completion of a grab operation.

If the callback is AL\_STDOUT, the userData pointer points to a string in memory, which was printed to stdout by the frame grabber. These callbacks can contain usefull diagnostics, but need not be processed for the library to operate correctly.

If the reason is AL\_GRAB\_TIMEOUT image data was not received from the hardware within the timeout interval (10 seconds).

#### Example:

```

int MyCallBack(int reason, void* userPtr, int index)

{

if(reason == AL_IMAGE_READY)

{

// new image grabbed

}

else if(reason == AL_GRAB_FINISHED)

{

// The buffer is full

}

}

```

alfmlSetCollBack(fgrab, MyCallBack, userPtr);

## AlfmlStartGrab

#### C Usage

#### Arguments

| Fgrab          | A valid handle to the board previously allocated with AlfmlOpen() function.                        |

|----------------|----------------------------------------------------------------------------------------------------|

| grabMode       | The type of acquisition to perform. Can be GRAB_CONTINUOUS or GRAB_ONE_SHOT.                       |

| imagesPerEvent | The number of images that are acquired before calling the Callback function with ImageReady event. |

| skipCount      | The number of frames to skip between each acquired image. A value of 0 acquires all the images.    |

#### Description

Starts a continuous acquisition. The grabMode parameter can have two values, which are defined, at the library header file:

AL\_GRAB\_CONTINUOUS - The board grab images continuously and when it reaches the end of the buffer, it continues placing the next image at the beginning of the frame buffer.

AL\_GRAB\_ONE\_SHOT - The board grabs images continuously and stops when the frame buffer is full. At the end it generates an AL\_GRAB\_FINISHED event.

During the grabbing the frame grabber can produce events to notify the application when new image is available. The value of the imagesPerEvent parameter determines the number of frames the board acquired before generating an event (AL\_IMAGE\_READY).

#### **Return Values:**

On success, this function returns zero value. On failure, this function returns an error code. To get extended error information, call AlfmlGetLastError().

#### Example:

## AlfmlStopGrab

#### C Usage

int AlfmlStopGrab(imdev\_t fgrab)

#### Arguments

| A valid handle to the board previously allocated with AlfmlOpen() function. |

|-----------------------------------------------------------------------------|

| • •                                                                         |

#### Description

Stops an acquisition in progress. Once this function stops an acquisition, you can restart the acquisition with the AlfmlStartGrab() function.

#### **Return Values:**

On success, this function returns zero value. On failure, this function returns an error code. To get extended error information, call AlfmlGetLastError().

After receiving the stop command, the frame grabber generates an AL\_GRAB\_FINISHED event.

#### Example:

#### AlfmlGetImage

#### C Usage

image\_t AlfmlGetImage(imdev\_t fgrab, int imageIndex)

#### Arguments

| fgrab      | A valid handle to the board previously allocated with AlfmIOpen() function. |

|------------|-----------------------------------------------------------------------------|

| imageIndex | The index of the image in the ring buffer.                                  |

#### Description

Returns an image from the ring acquisition buffer. Use this function to get access to the grabbed images.

#### **Return Values:**

On success, this function returns a variable of type image\_t. On failure, this function returns NULL.

#### Example:

image\_t img; int iLast;

iLast = AlfmlGetLastImageIndex(fgrab); img = AlfmlGetImage(fgrab, iLast);

## AlfmlGetLastImageIndex

#### C Usage

#### Arguments

| fgrab | A valid handle to the board previously allocated with |

|-------|-------------------------------------------------------|

|       | AlfmlOpen() function.                                 |

#### Description

Returns the index in the frames ring buffer of the last grabbed image.

#### **Return Values:**

Index of the last grabbed image.

#### Example:

| <pre>image_t img;</pre>                           |  |  |

|---------------------------------------------------|--|--|

| int iLast;                                        |  |  |

|                                                   |  |  |

| <pre>iLast = AlfmlGetLastImageIndex(fgrab);</pre> |  |  |

| <pre>img = AlfmlGetImage(fgrab, iLast);</pre>     |  |  |

|                                                   |  |  |

## **AlfmlGetFramesCount**

#### C Usage

int AlfmlGetFramesCount(imdev\_t fgrab)

#### Arguments

| Fgrab | A valid handle to the board previously allocated with |

|-------|-------------------------------------------------------|

|       | AlfmlOpen() function.                                 |

#### Description

Returns the number of frames grabbed since the start of an acquisition.

## AlfmlGetBufferSize

#### C Usage

int AlfmlGetBufferSize(imdev\_t fgrab)

#### Arguments

| Fgrab | A valid handle to the board previously allocated with |

|-------|-------------------------------------------------------|

|       | AlfmlOpen() function.                                 |

#### Description

Returns the number of frames allocated at the ring buffer.

## AlfmlSetChannel

#### C Usage

int AlfmlSetChannel(imdev\_t fgrab, int inputChannel)

#### Arguments

| Fgrab        | A valid handle to the board previously allocated with AlfmlOpen() function. |  |  |  |

|--------------|-----------------------------------------------------------------------------|--|--|--|

| inputChannel | Selected input channel.                                                     |  |  |  |

#### Description

Selects one of the video inputs to be active. The first channel is 0 and the last channel is according to the specified board been used. The default channel after calling AlfmlOpen() is channel 0.

#### **Return Values:**

On success, this function returns zero value. On failure, this function returns an error code. To get extended error information, call AlfmlGetLastError().

## AlfmlGetLastError

#### C Usage

int AlfmlGetLastError(imdev\_t fgrab)

#### Arguments

| 0 | A valid handle to the board previously allocated with AlfmIOpen() function. |  |  |  |  |

|---|-----------------------------------------------------------------------------|--|--|--|--|

|   |                                                                             |  |  |  |  |

#### Description

Returns the error code of the last FastMotion Library function executed.

#### **Return Values:**

This function returns the last error code and 0 if there is no pending error.

## AlfmlGetErrorStr

## C Usage

#### AlfmlGetErrorStr(int errorCode, char\* errStr)

#### Arguments

| errorCode | A valid handle to the board previously allocated with AlfmlOpen() function. |  |  |

|-----------|-----------------------------------------------------------------------------|--|--|

| errStr    | A storage for error message text.                                           |  |  |

## Description

This function returns the error text corresponding to an error code. The caller must allocate a minimum of 64 bytes for message storage before calling this function.

#### **Return Values:**

## 3. FAST-X UXGA FUNCTIONS

The Fast-X with the UXGA option has two additional functions in the AFML interface as well as several different functions supported by the firmware loaded by the FastMotion Library.

## 1.9 API Functions of the FastMotion UXGA Option Library

## AlfmlGetFlag

#### C Usage

unsigned long AlfmlGetFlag (imdev\_t fgrab, int cpu, int reg)

#### Arguments

| Fgrab | A valid handle to the board previously allocated with AlfmlOpen() function.                      |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|

| Сри   | The CPU instance number in a multi-CPU application.<br>Set this parameter to zero in most cases. |  |  |  |

| Reg   | A storage for error message text.                                                                |  |  |  |

#### Description

This function returns the contents of the 'Flag' register present in the UXGA version of the firmware. The registers contain diagnostic information about the internal functions of the firmware. There are 10 registers numbered 0 to 9. Providing an incorrect register number will return 0xBADDF00D, These Flag registers can change with revision of the software, so do not depend on the retaining any useful content.

#### **Return Values:**

This function returns the contents of the 'Flag' register present in the UXGA version of the firmware.

The registers contain:

| Reg # | Contents                                                                                                             |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0     | The write index of the shared memory area in host memory                                                             |  |  |  |  |  |  |

| 1     | The read index of the shared memory area in host memory                                                              |  |  |  |  |  |  |

| 2     | The write index of the internal buffer ring, which was last filled by the hardware.                                  |  |  |  |  |  |  |

| 3     | The read index of the internal buffer ring, which<br>was last started to DMA to the host shared<br>memory area.      |  |  |  |  |  |  |

| 4     | Time in microseconds sense the last interrupt from the hardware transferring an image into the board memory.         |  |  |  |  |  |  |

| 5     | Time from the last interrupt to when the deferred<br>procedure call completed processing the buffer<br>for channel 0 |  |  |  |  |  |  |

| 6     | Time from the last interrupt to when the deferred<br>procedure call completed processing the buffer<br>for channel 1 |  |  |  |  |  |  |

| 7     | Last line number in the source code being executed.                                                                  |  |  |  |  |  |  |

| 8     | Physical address of the shared memory area in host memory.                                                           |  |  |  |  |  |  |

| 9     | The offset from the base of SRAM area in the on board processor, to the control structure.                           |  |  |  |  |  |  |

# AlfmlSendCommand

## C Usage

int AlfmlGetFlag (imdev\_t fgrab, int cmd, int len, void \*d)

## Arguments

| fgrab | A valid handle to the board previously allocated with AlfmlOpen() function. |  |  |  |  |

|-------|-----------------------------------------------------------------------------|--|--|--|--|

| cmd   | Enum value defining the command being sent to the board.                    |  |  |  |  |

| len   | Length of parameter data pointed to by the void pointer 'd'                 |  |  |  |  |

| d     | Void pointer to parameter data.                                             |  |  |  |  |

#### Description

This function is provided for informational /diagnostic reasons, but it is an internal API not intended to be used by user applications. This function sends a command message to the processor on the target board (or boards) as determined by the enum value of 'cmd'. The command can also have parameter data which is provided for by the remaining arguments. The functionality of the commands are subject to change as this is an internal function.

#### **Return Values:**

This function returns zero if the message was sent successfully, non-zero if it was not sent successfully.

#### 1.10 Command Summary

The commands and parameters in the UXGA firmware are:

| Cmd # | Contents                                                         |  |  |  |  |

|-------|------------------------------------------------------------------|--|--|--|--|

| 256   | Select a channel. (0 or 1)                                       |  |  |  |  |

| 257   | Update trigger settings. Not used by the UXGA option.            |  |  |  |  |

| 258   | Select production of a focus image. Not used by the UXGA option. |  |  |  |  |

|       | Enable capturing. The following are the 'long' parameters:       |  |  |  |  |

|       | Grab mode (1=one shot 2=continuous)                              |  |  |  |  |

| 259   | ImagesPerInterrupt (usually set to 0, or one image per evt)      |  |  |  |  |

|       | Skip (usually 0, give every image, 1 give every other image)     |  |  |  |  |

|       |                                                                  |  |  |  |  |

| 260 | Cause the firmware to exit. Crash the program.                                                                                                                              |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 261 | Stop Capture. Parameter:<br>When (0=now, nz=when post trigger count<br>expires)                                                                                             |  |  |  |  |  |

| 262 | Draw digits of two counters on image. Parameter<br>Stop (0=stop 1=do it)<br>The two numbers are a time in microseconds,<br>and a frame index. Only on simulated image data. |  |  |  |  |  |

| 263 | Make simulated images.<br>Stop (0=stop 1=do it)                                                                                                                             |  |  |  |  |  |

| 264 | Trigger now. Stop capture after post trigger count expires.                                                                                                                 |  |  |  |  |  |

| 265 | Sent by firmware when images are not coming into the board.                                                                                                                 |  |  |  |  |  |

| 266 | Diagnostic message sent by board.                                                                                                                                           |  |  |  |  |  |

| 267 | Re-arm the trace buffer in the FPGA                                                                                                                                         |  |  |  |  |  |

| 268 | Adjusts the clock phase on the DMA channel<br>from the FPGA to the Stretch. Parameter -8 to +8<br>Should be -4. Don't mess with this.                                       |  |  |  |  |  |

| 269 | Set the serial baud rate.<br>Parameter selects the channel (0 or 1)                                                                                                         |  |  |  |  |  |

| 270 | Adjust the PLL divisor of the AD9888s<br>P1=Channel (0=ch0 1=ch1 2 -1=both)<br>P2=divisor (minus 1) see the AD9888 data sheet                                               |  |  |  |  |  |

| 271 | Adjust the clock phase AD9888s on the UXGA<br>board.<br>P1=Channel (0=ch0 1=ch1 2 -1=both)<br>P2=phase range is 0 to 31.                                                    |  |  |  |  |  |

| 272 | Change the input MUX setting for the selected<br>channel.<br>P1=Channel (0=ch0 1=ch1 2 -1=both)<br>P2=setting (0=A 1=B 2=Off)                                               |  |  |  |  |  |

| 273 | Set the PLL current of AD9888s<br>P1=Channel (0=ch0 1=ch1 2 -1=both)                                                                                                        |  |  |  |  |  |

|     | P2=setting                         |  |  |  |

|-----|------------------------------------|--|--|--|

|     | Set the PLL range of AD9888s       |  |  |  |

| 274 | P1=Channel (0=ch0 1=ch1 2 -1=both) |  |  |  |

|     | P2=setting                         |  |  |  |

## 4. UXGA CAPTURE CONTROL FILE CONTENT

The operation of the UXGA interface and the firmware has many parameters which are stored in an editable file. This file is called a capture control file '.cap'. The format of the file is much like a Windows INI file. A modification to the format is the inclusion of data type flags before the actual value of the parameter.

The format is a section header between two square brackets '[' or ']'. The section name should be less than 64 characters, the case is important. After a section header is a number of lines containing parameters and values. The format of a parameter line is the parameter name which is limited to 64 characters, followed by an equal size ('='), followed by one of the type flags 'int', 'float', or 'string'. Followed by the value, which must be less than 64 characters.

The capture file format also supports include files. The parameter '!include' by the file name, will cause the file to be read and processed. The number of levels of include supported is large, limited by the size of the stack.

The capture file format also supports conditional processing delimiters, '!if', '!else' and '!endif'. The token following the '!if' can be '0' or '1'.

Finally a comment token '#' provided. Characters from the '#' to the end of the line are ignored. DO NOT use the // as a comment character it causes big problems.

The capture file constructs a tree in memory with the root pointing to a linked list of section headers, which point to linked lists of parameters with their values. This structure is queried by the host software (alfml.dll) and by the board firmware. Some section headers may not apply to a particular board type. (Yes this was created before XML...)

Capture control files use the extent '.cap' but this is not required, they can have any file name.

#### 1.11 [Stretch] Section

This section informs the FastMotion Library which processor to load with what firmware. Firmware is matched to the options on the board. Typically this is not edited by a user.

#### 1.11.1 np = int 1

Number of processors in application. Normally this is one.

#### 1.11.2 select0 = int 1

This parameter selects whether a processor is included in the set controlled by FastMotion Library. The digit at the end of the parameter selects which processor, the value selects if this processor is to be used.

#### 1.11.3 prog0 = string "uxgaFastX.exe"

The parameter selects which firmware to load to the board. Firmware is matched to the options on the board. Typically this is not edited by a user.

#### 1.11.4 [FastMotion] Section

This section is descriptive and does not effect the operation of the hardware or software. This section is used by Fast Motion Application and is not used by the FastMotion Library.

#### 1.11.5 CameraName = string "Fx-sxga-60"

Camera model name.

#### 1.11.6 frame0 = string "1280,1024,60"

The width, height, and frame rate of the camera.

#### 1.11.7 line0 = string "1280x1024x24@60"

This is displayed in the selection dialog.

#### 1.11.8 line1 = string "Fast-X"

This is displayed in the selection dialog.

#### 1.11.9 DISPLAY\_SHIFT = int 0

This is used to shift the pixel values before they are displayed. Positive numbers mean left shift, negative numbers mean right shift. This is used by the application to select which bits are used to display an image.

#### 1.11.10 SIMULATE = int 0

This parameter controls various simulation functions in the various firmware. Typical it causes the firmware to generate images without a camera, to test the setup.

#### 1.11.11 **ANNOTATE = int 0**

This parameter controls if text is written to the image with various types of information. Typically the firmware adds a frame number and a time.

#### 1.11.12 INPUT\_CHANNELS = int 2

This parameter tells the Fast Motion Application how many channels are present in the current configuration.

#### 1.12 [PLL] Section

#### 1.12.1 PLL\_CONTROL = int -4

This parameter tunes the clock phase on the 200 MHz data channel between the FPGA and the Stretch processor. Do not change this.

#### 1.13 [BUFFER.1] Section

The Ping Pong settings should be used in applications which require images from more than one channel or mux setting. Ping Pong reduces the bandwidth to that of a single channel by alternating channels which are sampled. The alternation is done in a way that the time it takes for the AD9888 PLL to re-sync is masked by the other channel. To take images from all the inputs set Ping Pong Mux and Channel.

NOTE: IF A CHANNEL DOES NOT HAVE INPUT THE PING PONG WILL STOP ON THAT CHANNEL WAITING FOR A FRAME. BE SURE ALL THE SELECTABLE CHANNELS HAVE VIDEO INPUT.

#### 1.13.1 PING\_PONG\_CHANNEL = int 0

This parameter informs the UXGA firmware to switch back a forth between channel 1 and 2. This is used for monitoring applications to get data from many channels as fast as possible.

#### 1.13.2 **PING\_PONG\_MUX = int 0**

This parameter informs the UXGA firmware to switch through the input multiplexer channels for channel 0.

#### 1.14 [BUFFER.2] Section

#### 1.14.1 PING\_PONG\_MUX = int 0

This parameter informs the UXGA firmware to switch through the input multiplexer channels for channel 2.

#### 1.15 [AFML] Section

This section defines the size and kind of image the host would like to obtain from the board(s). In many applications this is not free to be changed. The format of the image must be RGB24 for the UXGA option. The size of the image can change to match the size of the video source.

- 1.15.1 HOST\_INPUT\_PIXELS\_PER\_LINE = int 1280

- 1.15.2 HOST\_INPUT\_LINES\_PER\_BUFFER = int 1024

- 1.15.3 HOST\_INPUT\_TYPE = string RGB24

#### 1.16 [UXGA.1] and [UXGA.2] Sections

This section controls the registers in the FPGA. The number at the end of the section name indicates the channel that is affected by this section.

#### 1.16.1 ENABLE = int 1

The enable bit control whether the channel will be used in this application.

#### 1.16.2 START\_PIXEL = int 358 WIDTH = int 1280 START\_LINE = int 20 END\_LINE = int 1043

These four parameters determine the ROI to be extracted from the input video. The value for the start pixel is in clock after the leading edge of horizontal sync. The start line is the first line in the image which has useful video. The end line parameter determines the last line that will be input from the image. The start and end parameters include the line or pixel they select.

#### 1.16.3 HS\_ACTIVE\_HI = int 1 VS\_ACTIVE\_LO = int 0 AUTO\_POLARITY = int 1

These values control the polarity of the sync signals. If auto polarity is set the other two parameters are ignored. Typically you should use auto polarity. Should auto polarity not perform as desired, the set it to zero, and select the polarity with the other two parameters. Note that the parameters name what the value 1 will select. So HS\_ACTIVE\_HI if one selects an active high HSYNC. Note that the two parameters HS\_ACTIVE\_HI and VS\_ACTIVE\_LO have opposite sense. For example if both syncs are active low then HS\_ACTIVE\_HI is zero and VS\_ACTIVE\_HI is one.

#### 1.16.4 INTERLACE = int 0

The interlace bit informs the FPGA that the input video is 2:1 interlaced. Note the ROI settings DO NOT change if the input is interlaced. The FPGA takes care of the even odd line counting.

#### 1.16.5 CAPTURE\_ENABLE = int 1

This bit enables video to be captured by the FPGA. Setting this to zero will prevent video from being captured on the selected channel, but the channel will be setup and ready to do it if the capture bit is changed.

#### 1.16.6 MONOCHROME = int 0

The monochrome bit causes the FPGA to only use the green input. The red and blue inputs will be ignored. The image in memory will be a GREY8 image rather than a RGB24 image.

# 1.16.7USEBUFFER1= int 1USEBUFFER2= int 1

These two bits control the buffer management. Both of these should be set to one.

#### 1.16.8 IGNORE\_STRIDE = int 0

This bit causes the DMA engine to do a linear DMA and not step to the next line start, at the end of a line. This should be zero.

#### 1.17 [Capture.1] and [Capture.2] Sections

These two sections define the input image to the firmware running on the board. These values are used to program the hardware, and define what is to be expected in memory when the hardware finishes a DMA.

#### 1.17.1 NUMBER\_OF\_BUFFERS = int 4

This defines the number of buffers to be used in the input circular chain of buffers. This is typically not changed.

#### 1.17.2 INPUT\_PIXELS\_PER\_LINE = int 1280

As the name says.

#### 1.17.3 INPUT\_LINES\_PER\_BUFFER = int 1024

This should be set to greater than (+1 or more) the number of lines in the image. If the value is too small a partial image will be captured, with the balance spilling into the next buffer.

#### 1.17.4 INPUT\_XOFFSET = int 0 INPUT\_YOFFSET = int 0

The value determines which line and pixel is the line that has useful image data. These are not the same values as those in the UXGA section, but apply to the image as provided by the hardware. This allows you to select a smaller area of the image to be transferred to the host.

#### 1.17.5 INPUT\_NX = int 1280 INPUT\_NY = int 1024

This value determines the width and height of the ROI being extracted from the image in memory. Typically these match the ROI settings of the UXGA section.

#### 1.17.6 INPUT\_PIXEL\_SIZE = int 3

This is the number of bytes in the pixel. It should be 3 or in the monochrome case it should be 1.

#### 1.17.7 INPUT\_PIXEL\_TYPE = string RGB24

This field determines the format of the pixel. RGB24 means LSB is red, middle byte is green and the MSB is blue. This field is GREY8 for the monochrome case.

#### 1.18 [AD9888B.1 and [AD9888B.2] Sections

The fields in this section define the register values to be programmed in the AD9888. One set of values for each AD9888. It is beyond the scope of this document to explain all these settings please refer to the Analog Devices data sheet for the AD9888B. These settings are important to the quality of the resulting images, and will required adjustment for different video sources. Typically you should only need to change the first four values to match your video source. For better color matches adjust the red, green and blue gains and offsets.

These values are example values taken from a 1280x1024 @ 60 Hz Toshiba laptop setting.

PLLDIV = int 1686 Range = int 2Current = int 4Phase = int 16ClampLoc = int 16ClampDur = int 64HsyncWidth = int 112 RedGain = int 128 GreenGain = int 128 BlueGain = int 128 RedOffset = int 128 GreenOffset = int 128 BlueOffset = int 128 VsyncOutSource = int 0 VsyncOverride = int 0 VsyncOutInvert = int 0 HsyncInSource = int 0 HsyncOverride = int 0HsyncOutInvert = int 0 HsyncInInvert = int 0 HsyncPolOverride = int 0 PowerUp = int 1 PowerMode = int 0 CoastPolarity = int 0CoastOverride = int 0Coast Select = int 1 Clamp Polarity = int 0 Clamp Source = int 0 MustBeOne = int 1 BlueClamp = int 0 RedClamp = int 0 SyncOnGreenThreshold = int 15 SyncSeparatorThreshold = int 32 PreCoast = int 0 PostCoast = int 0 ExternalClock = int 0 InputBandwidth = int 3 InputMux = int 0 Format422 = int 0ABInvert = int 0OutputMode = int 1 ChannelMode = int 1 MustBeZero = int 0MustBeOnes = int -1

## 5. THE AD9888 REGISTERS

The AD9888 is initialized and controlled by a set of registers that determine the operating modes. An external controller is employed to write and read the Control Registers through the 2-line serial interface port (I squared C). The information in this section is abstracted from the Analog Devices data sheet. You should obtain a copy of this data sheet. Search for AD9888 on Google.

| Hex<br>Address | Read and<br>Write or<br>Read Only | Bits | Default<br>Value | Register Name              | Function                                                                                                                                                                                                                  |

|----------------|-----------------------------------|------|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H            | RO                                | 7:0  |                  | Chip Revision              | An 8-bit register that represents the silicon revision level.<br>Revision 0 = 0000 0000.                                                                                                                                  |

| 01H            | R∕₩                               | 7:0  | 01101001         | PLL Div MSB                | This register is for Bits [11:4] of the PLL divider. Larger values mean the PLL operates at a faster rate. This register should be loaded first whenever a change is needed. (This will give the PLL more time to lock.)* |

| 02H            | R/W                               | 7:4  | 1101****         | PLL Div LSB                | Bits [7:4] LSBs of the PLL divider word.*                                                                                                                                                                                 |

| 03H            | R/W                               | 7:2  | 01*****          | VCO/CPMP                   | Bits [7:6] VCO Range. Selects VCO frequency range. (See PLL description.)                                                                                                                                                 |

|                |                                   |      | **001***         |                            | Bits [5:3] Charge Pump Current. Varies the current that drives the low-<br>pass filter. (See PLL description.)                                                                                                            |

| 04H            | R∕₩                               | 7:3  | 10000***         | Phase Adjust               | ADC Clock phase adjustment. Larger values mean more delay.<br>(1 LSB = T/32)                                                                                                                                              |

| 05H            | R∕₩                               | 7:0  | 00001000         | Clamp Placement            | Places the Clamp signal an integer number of clock periods after the trailing edge of the Hsync signal.                                                                                                                   |

| 06H            | R/W                               | 7:0  | 00010100         | Clamp Duration             | Number of clock periods that the Clamp signal is actively clamping.                                                                                                                                                       |

| 07 H           | R∕₩                               | 7:0  | 00100000         | Hsync Output<br>Pulsewidth | Sets the number of pixel clocks that HSOUT will remain active.                                                                                                                                                            |

| 08H            | R∕₩                               | 7:0  | 10000000         | Red Gain                   | Controls ADC input range (contrast) of each respective channel. Big<br>ger values give less contrast.                                                                                                                     |

| 09H            | R/W                               | 7:0  | 10000000         | Green Gain                 |                                                                                                                                                                                                                           |

| 0AH            | R/W                               | 7:0  | 10000000         | Blue Gain                  |                                                                                                                                                                                                                           |

| 0BH            | R∕₩                               | 7:1  | 1000000*         | Red Offset                 | Controls dc offset (brightness) of each respective channel. Bigger values decrease brightness.                                                                                                                            |

| 0CH            | R∕₩                               | 7:1  | 1000000*         | Green Offset               |                                                                                                                                                                                                                           |

| 0DH            | R/W                               | 7:1  | 1000000*         | Blue Offset                |                                                                                                                                                                                                                           |

|                            |                       |      |                  | Table V. Conti              | rol Register Map (continued)                                                                                                                                                                                                                                              |

|----------------------------|-----------------------|------|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read and<br>Hex<br>Address | Write or<br>Read Only | Bits | Default<br>Value | Register Name               | Function                                                                                                                                                                                                                                                                  |

| 0EH                        | R/W                   | 7:0  | 0******          | Sync Control                | Bit 7—Hsync Polarity Override. (Logic 0 = Polarity determined by chip,<br>Logic 1 = Polarity set by Bit 6 in Register 0EH.)                                                                                                                                               |

|                            |                       |      | *1*****          |                             | Bit 6—Hsync Input Polarity. Indicates to the PLL the polarity of the in<br>coming Hsync signal. (Logic 0 = active low, Logic 1 = active high.)                                                                                                                            |

|                            |                       |      | **0****          |                             | Bit 5—Hsync Output Polarity. (Logic 0 = Logic High Sync, Logic 1 =<br>Logic Low Sync).                                                                                                                                                                                    |

|                            |                       |      | ***0****         |                             | Bit 4—Active Hsync Override. If set to Logic 1, the user can select the Hsync to be used via Bit 3. If set to Logic 0, the active interface is selected via Bit 6 in Register 14H.                                                                                        |

|                            |                       |      | ****0***         |                             | Bit 3—Active Hsync Select. Logic 0 selects Hsync as the active sync.<br>Logic 1 selects Sync-on-Green as the active sync. Note: the indicated<br>Hsync will be used only if Bit 4 is set to Logic 1 or if both syncs are active<br>(Bits 1, 7 = Logic 1 in register 14H). |

|                            |                       |      | *****0**         |                             | Bit 2-Vsync Output Invert. (Logic 0 = Invert, Logic 1 = No Invert.)                                                                                                                                                                                                       |

|                            |                       |      | ******0*         |                             | Bit 1—Active Vsync Override. If set to Logic 1, the user can select the<br>Vsync to be used via Bit 0. If set to Logic 0, the active interface is selected<br>via Bit 3 in Register 14H.                                                                                  |

|                            |                       |      | *******0         |                             | Bit 0—Active Vsync Select. Logic 0 selects Raw Vsync as the output Vsync.<br>Logic 1 selects Sync Separated Vsync as the output Vsync. Note: The indi-<br>cated Vsync will be used only if Bit 1 is set to Logic 1.                                                       |

| 0FH                        | R/₩                   | 7:1  | 0******          |                             | Bit 7—Clamp Function. Chooses between Hsync for Clamp signal or<br>another external signal to be used for clamping. (Logic 0 = Hsync,<br>Logic 1 = Clamp.)                                                                                                                |

|                            |                       |      | *1*****          |                             | Bit 6—Clamp Polarity. Valid only with external Clamp signal. (Logic 0 = active high, Logic 1 selects active low.)                                                                                                                                                         |

|                            |                       |      | **0*****         |                             | Bit 5—COAST select. Logic 0 selects the coast input pin to be used for the PLL coast. Logic 1 selects Vsync to be used for the PLL coast.                                                                                                                                 |

|                            |                       |      | ***0****         |                             | Bit 4—COAST Polarity Override. (Logic 0 = Polarity determined by chip,<br>Logic 1 = Polarity set by Bit 3 in Register 0FH.)                                                                                                                                               |

|                            |                       |      | ****1***         |                             | Bit 3—COAST Polarity. Changes polarity of external COAST signal.<br>(Logic = 0 = active low, Logic 1 = active high.)                                                                                                                                                      |

|                            |                       |      | *****1**         |                             | Bit 2—Seek Mode Override. (Logic 1 = allow low-power mode, Logic 0 = disallow low power mode.)                                                                                                                                                                            |

|                            |                       |      | *****1*          |                             | Bit 1— $\overline{PWRDN}$ . Full Chip Power-Down, active low. (Logic 0 = Full Chip Power-Down, Logic 1 = normal.)                                                                                                                                                         |

| 10H                        | R/W                   | 7:3  | 01111***         | Sync-on-Green<br>Thr eshold | Sync-on-Green Threshold — Sets the voltage level of the Sync-on-Green slicer's comparator.                                                                                                                                                                                |

|                            |                       |      | *****0**         |                             | Bit 2—Red Clamp Select – Logic 0 selects clamp to ground. Logic 1 selects<br>clamp to midscale (voltage at Pin 9).                                                                                                                                                        |

|                            |                       |      | ******0*         |                             | Bit 1—Blue Clamp Select – Logic 0 selects clamp to ground. Logic 1 selects<br>clamp to midscale (voltage at Pin 24).                                                                                                                                                      |

|                            |                       |      | ******0          |                             | Bit 0-Must be set to 1 for proper operation.                                                                                                                                                                                                                              |

| 11H                        | R∕₩                   | 7:0  | 00100000         | Sync Separator<br>Threshold | Sync Separator Threshold – Sets how many internal 5 MHz clock periods<br>the sync separator will count to before toggling high or low. This should be<br>set to some number greater than the maximum Hsync or equalization<br>pulsewidth.                                 |

| 12H                        | R/₩                   | 7:0  | 00000000         | Pre-COAST                   | Pre-COAST- Sets the number of Hsync periods that coast becomes active prior to Vsync.                                                                                                                                                                                     |

| 13H                        | R/₩                   | 7:0  | 00000000         | Post-COAST                  | Post-COAST – Sets the number of Hsync periods that coast stays active following Vsyn c.                                                                                                                                                                                   |

#### Table V. Control Register Map (continued)

| Hex<br>Address | Read and<br>Write or<br>Read Only | Bits | Default<br>Value | Register Name | Function                                                                                                                                                 |

|----------------|-----------------------------------|------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14H            | RO                                | 7:0  |                  | Sync Detect   | Bit 7—Hsync Detect. It is set to Logic 1 if Hsync is present on the analog<br>interface, else it is set to Logic 0.                                      |

|                |                                   |      |                  |               | Bit 6—AHS: Active Hsync. This bit indicates which analog Hsync is being<br>used. (Logic 0 = Hsync input pin, Logic 1 = Hsync from sync-on-green.)        |

|                |                                   |      |                  |               | Bit 5-Input Hsync Polarity Detect. (Logic 0 = active low, Logic 1 = active high.)                                                                        |

|                |                                   |      |                  |               | Bit 4—Vsync detect. It is set to Logic 1 if Vsync is present on the analog interface, else it is set to Logic 0.                                         |

|                |                                   |      |                  |               | Bit 3—AVS: Active Vsync. This bit indicates which analog Vsync is being used. (Logic 0 = Vsync input pin, Logic 1 = Vsync from sync separator.)          |

|                |                                   |      |                  |               | Bit 2—Output Vsync Polarity Detect. (Logic 0 = active high, Logic 1 = active low.)                                                                       |

|                |                                   |      |                  |               | Bit 1—Sync-on-Green Detect. It is set to Logic 1 if sync is present on the green video input, else it is set to 0.                                       |

|                |                                   |      |                  |               | Bit 0—Input COAST Polarity Detect. (Logic 0 = active low, Logic 1 = active high.)                                                                        |

| 15H            | R/W                               | 7:0  | 1******          |               | Bit 7—Channel Mode. Determines single-channel or dual-channel output<br>mode. (Logic 0 = single-channel mode, Logic 1 = dual-channel mode.)              |

|                |                                   |      | *1*****          |               | Bit 6—Output Mode. Determine interleaved or parallel output mode.<br>(Logic 0 = interleaved mode, Logic 1 = parallel mode.)                              |

|                |                                   |      | **0*****         |               | Bit 5—A/B Invert. Determines which port outputs the first data byte after<br>Hsync. (Logic 0 = A port, Logic 1 = B port.)                                |

|                |                                   |      | ***0****         |               | Bit 4-4:2:2 Output Formatting Mode.                                                                                                                      |

|                |                                   |      | ****0***         |               | Bit 3-Input Mux Control.                                                                                                                                 |

|                |                                   |      | *****11*         |               | Bits [2:1]—Input Bandwidth.                                                                                                                              |

|                |                                   |      | *******0         |               | Bit 0—External Clock. Shuts down PLL and allows external clock to drive the part. (Logic 0 = use internal PLL, Logic 1 = bypassing of the internal PLL.) |

| 16H            | R/W                               | 7:0  | 11111111         | Test Register | Must be set to 11111110 for proper operation.                                                                                                            |

| 17H            | R/W                               | 7:3  | 00000000         | Test Register | Must be set to default for proper operation.                                                                                                             |

| 18H            | RO                                | 7:0  |                  | Test Register |                                                                                                                                                          |

| 19H            | RO                                | 7:0  |                  | Test Register |                                                                                                                                                          |

#### Table V. Control Register Map (continued)

\*The AD9888 only updates the PLL divide ratio when the LSBs are written to (Register 02H).

#### AD9888 CONTROL REGISTER DETAIL

#### 1.19.1 Reg[OO] Bit(s)[7-O] Chip Revision

Register 00 is an 8-bit register that represents the silicon revision.

Revision 0 = 0000 0000,

Revision 1 = 0000 0001.

#### 1.19.2 PLL DIVIDER CONTROL

#### 1.19.3 Reg[O1] Bit(s)[7-O] PLL Divide Ratio MSBs

The eight most significant bits of the 12-bit PLL divide ratio PLLDIV. (The operational divide ratio is PLLDIV + 1.) The PLL derives a master clock from an incoming Hsync signal. The master clock frequency is then divided by an integer value, such that the output is phase-locked to Hsync. This PLLDIV value determines the number of pixel times (pixels plus horizontal blanking overhead) per line. This is typically 20% to 30% more than the number of active pixels in the display. The 12-bit value of the PLL divider supports divide ratios from 2 to 4095. The higher the value loaded in this register, the higher the resulting clock frequency with respect to a fixed Hsync frequency. VESA has established standard timing specifications that will assist in determining the value for PLLDIV as a function of horizontal and vertical display resolution and frame rate (Table IV). However, many computer systems do not conform precisely to the recommendations, and these numbers should be used only as a guide. The display system manufacturer should provide automatic or manual means for optimizing PLLDIV. An incorrectly set

PLLDIV will usually produce one or more vertical noise bars on the display. The greater the error, the greater the number of bars produced. The power-up default value of PLLDIV is 1693 (PLLDIVM = 69H, PLLDIVL = DxH). The AD9888 updates the full divide ratio only when the LSBs are changed. Writing to this register by itself will not trigger an update.

#### Reg[O2] Bit(s)[7-4] PLL Divide Ratio LSBs 1.19.4

The four least significant bits of the 12-bit PLL divide ratio PLLDIV. The operational divide ratio is PLLDIV + 1. The power-up default value of PLLDIV is 1693 (PLLDIVM = 69H, PLLDIVL = DxH). The AD9888 updates the full divide ratio only when this register is written to.

#### CLOCK GENERATOR CONTROL 1.19.5

#### 1.19.6 Reg[O3] Bit(s)[7-6] VCO Range Select

Two bits that establish the operating range of the clock generator. VCORNGE must be set to correspond with the desired operating frequency (incoming pixel rate). The PLL gives the best jitter performance at high frequencies. For this reason, in order to output low pixel rates and still get good jitter performance, the PLL actually operates at a higher frequency but then divides down the clock rate afterwards. Table VI shows the pixel rates for each VCO range setting. The PLL output divisor is automatically selected with the VCO range setting. The power-up default value is 01.

| VCORNGE | Pixel Rate Range |

|---------|------------------|

| 00      | 10 - 41 MHz      |

| 01      | 41 - 82 MHz      |

| 10      | 82 - 150 MHz     |

| 11      | >150 MHz         |

#### 1.19.7 Reg[O3] Bit(s)[5-3] Charge Pump Current

Three bits that establish the current driving the loop filter in the clock generator. CURRENT must be set to correspond with the desired operating frequency (incoming pixel rate). The power-up default value is CURRENT = 001.

| Table VII. Charge Pump Currents |              |  |

|---------------------------------|--------------|--|

| Range                           | Current (µA) |  |

| 000                             | 50           |  |

| 001                             | 100          |  |

| 010                             | 150          |  |

| 011                             | 250          |  |

| 100                             | 350          |  |

| 101                             | 500          |  |

| 110                             | 750          |  |

|                                 |              |  |

## 1.19.8 Reg[O4] Bit(s)[7-3] Clock Phase Adjust

Register 04 bits 7 to 3 is a 5-bit value that adjusts the sampling phase in 32 steps across one pixel time. Each step represents an 11.25° shift in sampling phase. The power-up default value is 16.

#### 1.19.9 CLAMP TIMING

#### 1.19.10 Reg[O5] Bit(s)[7-O] Clamp Placement

Register 05 is an 8-bit register that sets the position of the internally generated clamp. When the external clamp control bit is set to 0, a clamp signal is generated internally, at a position established by the clamp placement and for a duration set by the clamp duration. Clamping is started (Clamp Placement) pixel periods after the trailing edge of Hsync. The clamp placement may be programmed to any value up to 255, except 0. The clamp should be placed during a time that the input signal presents a stable black-level reference, usually the back porch period between Hsync and the image. When the external clamp control bit is set to 1, this register is ignored.

#### 1.19.11 Reg[O6] Bit(s)[7-O] Clamp Duration

Register 06 is an 8-bit register that sets the duration of the internally generated clamp. When the external clamp control bit is set to 0, a clamp signal is generated internally, at a position established by the clamp placement and for a duration set by the clamp duration. Clamping is started (Clamp Placement) pixel periods after the trailing edge of Hsync, and continues for (Clamp Duration) pixel periods. The clamp duration may be programmed to any value between 1 and 255. A value of 0 is not supported. For the best results, the clamp duration should be set to include the majority of the black reference signal time that follows the Hsync signal trailing edge. Insufficient clamping time can produce brightness changes at the top of the screen, and a slow recovery from large changes in the Average Picture Level (APL), or brightness. When the external clamp control bit is set to 1, this register is ignored.

#### 1.19.12 HSYNC PULSE WIDTH

#### 1.19.13 Reg[O7] Bit(s)[7-O] Hsync Output Pulse width

Register 07 is an 8-bit register that sets the duration of the Hsync output pulse.

The leading edge of the Hsync output is triggered by the internally generated, phase adjusted PLL feedback clock. The AD9888 then counts a number of pixel clocks equal to the value in this register. This triggers the trailing edge of the Hsync output, which is also phase adjusted.

#### 1.19.14 INPUT GAIN

#### 1.19.15 Reg[O8] Bit(s)[7-O] Red Channel Gain Adjust

Register 08 is an 8-bit word that sets the gain of the RED channel. The AD9888 can accommodate input signals with a full-scale range of between 0.5 V and 1.0 V p-p. Setting REDGAIN to 255 corresponds to an input range of 1.0 V. A REDGAIN of 0 establishes an input range of 0.5 V. Note that increasing REDGAIN results in the picture having less contrast (the input signal uses fewer of the available converter codes). See Figure 2.

#### 1.19.16 Reg[O9] Bit(s)[7-O] Green Channel Gain Adjust

An 8-bit word that sets the gain of the GREEN channel. See REDGAIN (08).

#### 1.19.17 Reg[OA] Bit(s)[7-O] Blue Channel Gain Adjust

An 8-bit word that sets the gain of the BLUE channel. See REDGAIN (08).

#### 1.19.18 INPUT OFFSET

#### 1.19.19 Reg[OB] Bit(s)[7-1] Red Channel Offset Adjust

A 7-bit offset binary word that sets the dc offset of the RED channel. One LSB of offset adjustment equals approximately one LSB change in the ADC offset. Therefore, the absolute magnitude of the offset adjustment scales as the gain of the channel is changed. A nominal setting of 63 results in the channel nominally clamping the back porch (during the clamping interval) to code 00. An offset setting of 127 results in the channel clamping to code 64 of the ADC. An offset setting of 0 clamps to code –63 (off the bottom of the range). Increasing the value of Red Offset decreases the brightness of the channel.

#### 1.19.20 Reg[OC] Bit(s)[7-1] Green Channel Offset Adjust

A 7-bit offset binary word that sets the dc offset of the GREEN channel. See REDOFST (0B).

#### 1.19.21 Reg[OD] Bit(s)[7-1] Blue Channel Offset Adjust

A 7-bit offset binary word that sets the dc offset of the BLUE channel. See REDOFST (0B).

#### 1.19.22 Reg[OE] Bit(s)[7] Hsync Input Polarity Override

This register is used to override the internal circuitry that determines the polarity of the Hsync signal going into the PLL.

#### Table VIII. Hsync Input Polarity Override Settings

#### Override Bit Result

- 0 Hsync Polarity Determined by Chip

- 1 Hsync Polarity Determined by

User

The default for Hsync polarity override is 0 (polarity determined by chip).

#### 1.19.23 Reg[OE] Bit(s)[6]

Hsync Input Polarity

A bit that must be set to indicate the polarity of the Hsync signal that is applied to the PLL Hsync input.

HSPOL

#### Table IX. Hsync Input Polarity Settings

| HSPO<br>L | Function       |

|-----------|----------------|

| 0         | Active Low     |

| 1         | Active<br>High |

Active Low means the leading edge of the Hsync pulse is negative-going. All timing is based on the leading edge of Hsync, which is the falling edge. The rising edge has no effect. Active High means the leading edge of the Hsync pulse is positive-going. This means that timing will be based on the leading edge of Hsync, which is now the rising edge. The device will operate if this bit is set incorrectly, but the internally generated clamp position, as established by Clamp Placement (Register 05H), will not be placed as expected, which may generate clamping errors. The power-up default value is HSPOL = 1.

## 1.19.24 Reg[OE] Bit(s)[5] Hsync Output Polarity

One bit that determines the polarity of the Hsync output and the SOG output. Table X shows the effect of this option. SYNC indicates the logic state of the sync pulse. The default setting for this register is 0.

#### Table X. Hsync Output Polarity Settings

| Setting | SYNC                        |

|---------|-----------------------------|

| 0       | Logic 1 (Positive Polarity) |

| 1       | Logic 0 (Negative Polarity) |

#### 1.19.25 Reg[OE] Bit(s)[4] Active Hsync Override

This bit is used to override the automatic Hsync selection. To override, set this bit to Logic 1. When overriding, the active Hsync is set via Bit 3 in this register. The default for this register is 0.

Table XI. Active Hsync Override Settings

| Override | Result                                           |

|----------|--------------------------------------------------|

| 0        | Auto determines the active interface.            |

| 1        | Override, Bit 3, determines the active interface |

#### 1.19.26 Reg[0E] Bit(s)[3] Active Hsync Select

This bit is used under two conditions. It is used to select the active Hsync when the override bit is set (Bit 4). Alternately, it is used to determine the active Hsync when not overriding but both Hsyncs are detected. The default for this register is 0.

Table XII. Active Hsync Select Settings

| Select | Result              |

|--------|---------------------|

| 0      | Hsync Input         |

| 1      | Sync-on-Green Input |

## 1.19.27 Reg[0E] Bit(s)[2] Vsync Output Invert

A bit that inverts the polarity of the Vsync output. Table XIII shows the effect of this option. The default setting for this register is 0.

#### Table XIII. Vsync Output Polarity Settings

| Setting | SYNC         |

|---------|--------------|

| 0       | Invert       |

| 1       | Don't Invert |

#### 1.19.28 Reg[0E] Bit(s)[1] Active Vsync Override

This bit is used to override the automatic Vsync selection. To override, set this bit to Logic 1. When overriding, the active interface is set via Bit 0 in this register. The default for this register is 0.

#### Table XIV. Active Vsync Override Settings

| Override | Result                                       |

|----------|----------------------------------------------|

| 0        | Auto determines the active Vsync.            |

| 1        | Override, Bit 0 determines the active Vsync. |

This bit is used to select the active Vsync when the over ride bit is set (Bit 1). The default for this register is 0.

#### Table XV. Active Vsync Select Settings

| Select | Result                |

|--------|-----------------------|

| 0      | VSYNC Input           |

| 1      | Sync Separator output |

#### 1.19.30 Reg[0F] Bit(s)[7] Clamp Input Signal Source